# Parallel Interface, Multimedia Audio Codec

# **Features**

- Windows Sound System<sup>TM</sup> Compatible Codec

- ADPCM Compression/Decompression

- Extensive Software Support

- MPC Level 2 Compatible Mixer

- Dual DMA Registers support Full Duplex Operation

- On-Chip FIFOs for higher performance

- Selectable Serial Audio Data Port

- Pin Compatible with CS4231/CS4248

# **General Description**

The CS4231A includes stereo 16-bit audio converters and complete on-chip filtering for record and playback of 16-bit audio data. In addition, analog mixing and programmable gain and attenuation are included to provide a complete audio subsystem. A selectable serial port can pass audio data to and from DSPs or ASICs. Crystal-developed high-performance software drivers for various operating systems are available that support all the CS4231A features including full duplex transfers. The CS4231A is a pin compatible upgrade to the CS4231 and CS4248.

#### ORDERING INFORMATION:

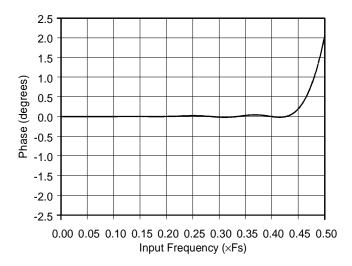

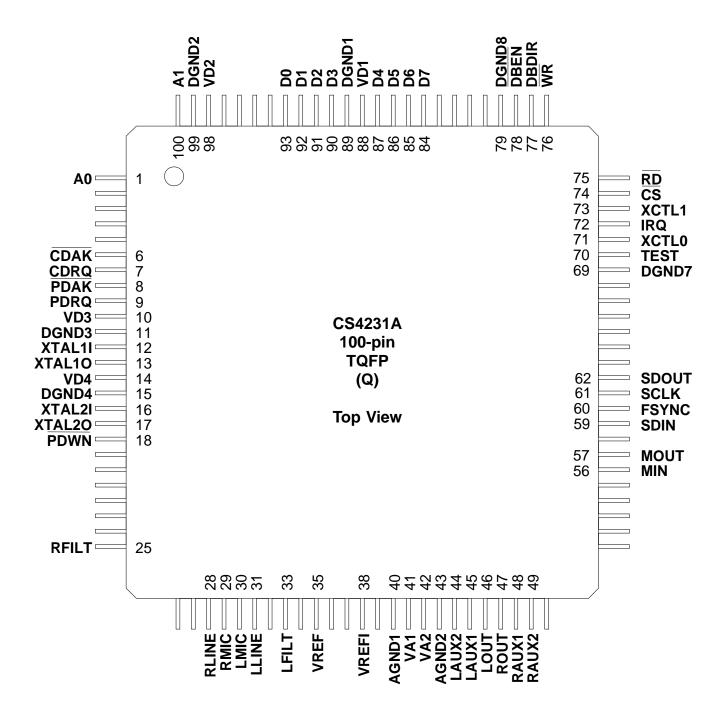

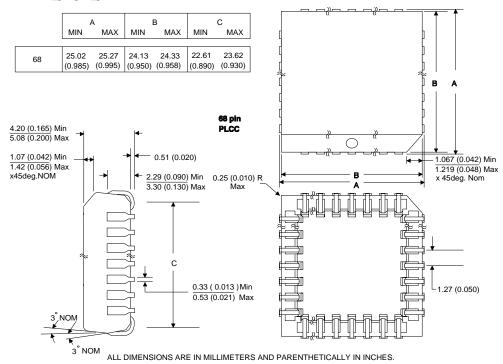

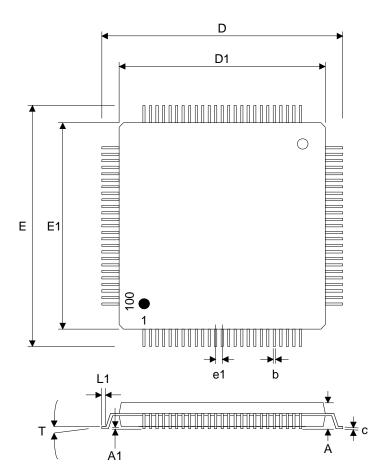

CS4231A-KL 0 to 70°C 68-pin PLCC CS4231A-KQ 0 to 70°C 100-pin TQFP

Preliminary Product Information

This document contains information for a new product. Crystal Semiconductor reserves the right to modify this product without notice.

# **TABLE OF CONTENTS:**

| CS4231A TECHNICAL SPECIFICATIONS        |    |

|-----------------------------------------|----|

| GENERAL DESCRIPTION                     |    |

| Enhanced Functions (MODE 2)             |    |

| Mixer Attenuation Control on Line Input |    |

| ANALOG HARDWARE DESCRIPTION             |    |

| Analog Inputs                           |    |

| Line-Level Inputs plus MPC Mixer        |    |

| Microphone Level Inputs                 |    |

| Mono Input with Attenuation and Mute    |    |

| Analog Outputs                          |    |

| Mono Output with Mute Control           |    |

| Miscellaneous Analog Signals            |    |

| DIGITAL HARDWARE DESCRIPTION            |    |

| Parallel Data Interface                 |    |

| FIFOs                                   |    |

| High Current Data Bus Drivers           |    |

| PIO Registers Interface                 |    |

| DMA Interface                           |    |

| Dual DMA Channel Mode                   |    |

| Single DMA Channel (SDC) Mode           |    |

| Serial Audio Data Port                  |    |

| Miscellaneous Signals                   |    |

| Crystals/Clocks                         |    |

| Power Down - PDWN                       |    |

| DBEN/DBDIR                              |    |

| SOFTWARE DESCRIPTION                    |    |

| Power-Down and Initialization           |    |

| Calibration Modes                       |    |

| Changing Sampling Rate                  |    |

| Changing Audio Data Formats             |    |

| Audio Data Formats                      |    |

| 16-bit Signed                           |    |

| 8-bit Unsigned                          |    |

| 8-bit Companded                         |    |

| ADPCM Compression/Decompression         |    |

| DMA Registers                           |    |

| Playback DMA Registers                  |    |

| Capture DMA Registers                   |    |

| Digital Loopback                        |    |

| Timer Registers                         |    |

| Interrupts                              |    |

| Error Conditions                        | 27 |

| CS4231A REGISTER MAPPING         |            | .28 |

|----------------------------------|------------|-----|

| Physical Mapping                 |            | .28 |

| Index Address Register           | . (R0)     | .29 |

| Index Data Register              | . (R1)     | .29 |

| Status Register                  | . (R2, RO) | .29 |

| Capture I/O Data Register        | . (R3, RO) | .30 |

| Playback I/O Data Register       | . (R3, WO) | .31 |

| Left ADC Input Control           | . (IO)     | .31 |

| Right ADC Input Control          | . (I1)     | .31 |

| Left Auxiliary #1 Input Control  | . (I2)     | .31 |

| Right Auxiliary #1 Input Control | . (I3)     | .32 |

| Left Auxiliary #2 Input Control  | . (I4)     | .32 |

| Right Auxiliary #2 Input Control | . (I5)     | .32 |

| Left DAC Output Control          | . (I6)     | .32 |

| Right DAC Output Control         | . (I7)     | .32 |

| Fs and Playback Data Format      | . (18)     | .33 |

| Interface Configuration          | . (19)     | .34 |

| Pin Control                      | . (I10)    | .35 |

| Error Status and Initialization  | •          |     |

| MODE and ID                      | . (I12)    | .36 |

| Loopback Control                 | . (I13)    | .36 |

| Playback Upper Base              | . (I14)    | .36 |

| Playback Lower Base              | . (I15)    | .36 |

| Alternate Feature Enable I       | . (I16)    | .37 |

| Alternate Feature Enable II      | . (I17)    | .37 |

| Left Line Input Control          | . (I18)    | .37 |

| Right Line Input Control         | . (I19)    | .40 |

| Timer Lower Base                 | . (I20)    | .40 |

| Timer Upper Base                 | . (I21)    | .40 |

| Alternate Feature Enable III     | . (I23)    | .40 |

| Alternate Feature Status         |            |     |

| Version/ Chip ID                 | . (I25)    | .41 |

| Mono Input & Output Control      | . (I26)    | .41 |

| Capture Data Format              | . (I28)    | .42 |

| Capture Upper Base               | . (I30)    | .42 |

| Capture Lower Base               | , ,        |     |

| GROUNDING AND LAYOUT             |            |     |

| COMPATIBILITY WITH AD1848        |            |     |

| ADC/DAC FILTER RESPONSE PLO      |            |     |

| PIN DESCRIPTIONS                 |            |     |

| PARAMETER DEFINITIONS            |            |     |

| APPENDIX A                       |            |     |

| PACKAGE DIMENSION                |            |     |

| CDB4231/4248 Data Sheet          |            | .57 |

**ANALOG CHARACTERISTICS** ( $T_A = 25$  °C; VA1, VA2, VD1-VD4 = +5V; Input Levels: Logic 0 = 0V, Logic 1 = VD1-VD4; 1 kHz Input Sine wave; Conversion Rate = 48 kHz;

Measurement Bandwidth is 10 Hz to 20 kHz, 16-bit linear coding.)

| Paramet                              | Symbol                                                                    | Min        | Тур                   | Max                  | Units              |                                                       |

|--------------------------------------|---------------------------------------------------------------------------|------------|-----------------------|----------------------|--------------------|-------------------------------------------------------|

| Analog Input Characteristics - N     | Minimum Gain Setting (0dB)                                                | unless oth | nerwise sp            | ecified.             |                    |                                                       |

| ADC Resolution                       | (Note 1)                                                                  |            | 16                    |                      |                    | Bits                                                  |

| ADC Differential Nonlinearity        | (Note 1)                                                                  |            |                       |                      | ±0.5               | LSB                                                   |

| Instantaneous Dynamic Range          | Line Inputs (Note 2) Mic Inputs                                           | IDR        | 80<br>72              | 85<br>77             |                    | dB<br>dB                                              |

| Total Harmonic Distortion            | Line Inputs<br>Mic Inputs                                                 | THD        |                       | 0.006<br>0.01        | 0.02<br>0.025      | %<br>%                                                |

| Signal-to-Intermodulation Distortion | n                                                                         |            |                       | 90                   |                    | dB                                                    |

| Interchannel Isolation               | Line to Line Inputs<br>Line to Mic Inputs<br>Line-to-AUX1<br>Line-to-AUX2 |            |                       | 80<br>80<br>90<br>90 |                    | dB<br>dB<br>dB<br>dB                                  |

| Interchannel Gain Mismatch           | Line Inputs<br>Mic Inputs                                                 |            |                       |                      | 0.5<br>0.5         | dB<br>dB                                              |

| Programmable Input Gain Span         | Line Inputs                                                               |            | 21.5                  | 22.5                 |                    | dB                                                    |

| Gain Step Size                       |                                                                           |            | 1.3                   | 1.5                  | 1.7                | dB                                                    |

| ADC Offset Error                     | 0 dB gain                                                                 |            |                       | 10                   | 100                | LSB                                                   |

| Full Scale Input Voltage:            | (MGE=1) MIC Inputs<br>(MGE=0) MIC Inputs<br>E, AUX1, AUX2, MIN Inputs     |            | 0.266<br>2.66<br>2.66 | 0.29<br>2.9<br>2.9   | 0.31<br>3.1<br>3.1 | V <sub>pp</sub><br>V <sub>pp</sub><br>V <sub>pp</sub> |

| Gain Drift                           |                                                                           |            |                       | 100                  |                    | ppm/°C                                                |

| Input Resistance                     | (Note 1)                                                                  |            | 20                    |                      |                    | kΩ                                                    |

| Input Capacitance                    | (Note 1)                                                                  |            |                       |                      | 15                 | pF                                                    |

Notes: 1. This specification is guaranteed by characterization, no production testing.

Windows and Windows Sound System are registered trademarks of Microsoft Corporation.

Specifications are subject to change without notice.

<sup>2.</sup> MGE = 1 and a 10  $\mu$ F capacitor on the VREF pin.

<sup>\*</sup>Parameter definitions are given at the end of this data sheet.

# **ANALOG CHARACTERISTICS** (Continued)

| Para                          | meter*                  |                                                                                        | Symbol        | Min        | Тур                          | Max                  | Units                |

|-------------------------------|-------------------------|----------------------------------------------------------------------------------------|---------------|------------|------------------------------|----------------------|----------------------|

| Analog Output Characteris     | tics - Minimum          | Attenuation (0dB)                                                                      | ); unless otl | herwise sp | ecified.                     |                      |                      |

| DAC Resolution                |                         |                                                                                        |               | 16         |                              |                      | Bits                 |

| DAC Differential Nonlinearity |                         | (Note 1)                                                                               |               |            |                              | ±0.5                 | LSB                  |

| Dynamic Range                 | -Total<br>-Instantaneou | All Outputs                                                                            | TDR<br>IDR    | 80         | 95<br>85                     |                      | dB<br>dB             |

| Total Harmonic Distortion     |                         | (Note 3)                                                                               | THD           |            | 0.01                         | 0.02                 | %                    |

| Signal-to-Intermodulation Dis | tortion                 |                                                                                        |               |            | 85                           |                      | dB                   |

| Interchannel Isolation        | Line Out                | (Note 3)                                                                               |               |            | 95                           |                      | dB                   |

| Interchannel Gain Mismatch    |                         | Line Out                                                                               |               |            | 0.1                          | 0.5                  | dB                   |

| Voltage Reference Output      |                         |                                                                                        |               | 2.0        | 2.2                          | 2.35                 | V                    |

| Voltage Reference Output Co   | urrent                  | (Note 4)                                                                               |               |            | 100                          |                      | μΑ                   |

| DAC Programmable Attenuat     | ion Span                |                                                                                        |               | 93         | 94.5                         |                      | dB                   |

| DAC Attenuation Step Size     | -82.                    | 0 dB to -81 dB<br>5 dB to -94.5 dB                                                     |               | 1.3<br>1.0 | 1.5<br>1.5                   | 1.7<br>2             | dB<br>dB             |

| DAC Offset Voltage            |                         |                                                                                        |               |            | 1                            | 10                   | mV                   |

| Full Scale Output Voltage:    | OLB = 0<br>OLB = 1      | (Notes 3, 5)<br>OUT, MOUT                                                              |               | 1.8<br>2.6 | 2.0<br>2.8                   | 2.25<br>3.2          | $V_{pp} \ V_{pp}$    |

| Gain Drift                    |                         |                                                                                        |               |            | 100                          |                      | ppm/°C               |

| Deviation from Linear Phase   |                         | (Note 1)                                                                               |               |            |                              | 1                    | Degree               |

| External Load Impedance       |                         |                                                                                        |               | 10         |                              |                      | kΩ                   |

| Mute Attenuation (0 dB)       |                         |                                                                                        |               | 80         |                              |                      | dB                   |

| Total Out-of-Band Energy      | 0.6xFs to 100           | kHz (Note 1)                                                                           |               |            |                              | -45                  | dB                   |

| Audible Out-of-Band Energy    | 0.6xFs to 22            | kHz (Fs=8kHz)                                                                          |               |            |                              | -60                  | dB                   |

| Power Supply                  |                         |                                                                                        |               |            |                              |                      |                      |

| Power Supply Current          | A<br>Dig                | Digital, Operating<br>nalog, Operating<br>Total<br>ital, Power Down<br>log, Power Down |               |            | 55<br>43<br>98<br>0.1<br>0.8 | 65<br>60<br>120<br>1 | mA<br>mA<br>mA<br>mA |

| Power Supply Rejection        | 1 kHz                   | (Note 1)                                                                               |               | 40         |                              |                      | dB                   |

- Notes: 3. 10 k $\Omega$ , 100 pF load.

- 4. DC current only. If dynamic loading exists, then the voltage reference output must be buffered or the performance of ADCs and DACs will be degraded.

- 5. All mixer and output gain tables assume the output level bit, OLB, in indirect register 16 (I16) is set, wherein the input and output full scale values are equal. When OLB=0, the output value is 3 dB below the input value, given no gain or attenuation.

# **AUXILIARY INPUT MIXERS** (TA = 25 °C; VA1, VA2, VD1-VD4 = +5V;

Input Levels: Logic 0 = 0V, Logic 1 = VD1-VD4; 1 kHz Input Sine wave)

| Pa                    | Parameter                     |  |            | Тур        | Max        | Units    |

|-----------------------|-------------------------------|--|------------|------------|------------|----------|

| Mixer Gain Range Span | LINE, AUX1, AUX2 (Note 6) MIN |  | 45<br>42   | 46.5<br>45 |            | dB<br>dB |

| Step Size             | LINE, AUX1, AUX2<br>MIN       |  | 1.3<br>2.3 | 1.5<br>3.0 | 1.7<br>3.4 | dB<br>dB |

Notes: 6. All mixer gain values assume OLB=1. If OLB=0, the analog output will be 3 dB below listed settings.

# **ABSOLUTE MAXIMUM RATINGS** (AGND, DGND = 0V, all voltages with respect to 0V.)

|                        | Parameter            | Symbol             | Min          | Max        | Units |

|------------------------|----------------------|--------------------|--------------|------------|-------|

| Power Supplies:        | Digital<br>Analog    | VD1-VD4<br>VA1,VA2 | -0.3<br>-0.3 | 6.0<br>6.0 | V     |

| Input Current per Pin  | (Except Supply Pins) |                    | -10.0        | +10.0      | mA    |

| Output Current per Pin | (Except Supply Pins) |                    | -50          | +50        | mA    |

| Analog Input Voltage   |                      |                    | -0.3         | VA+0.3     | V     |

| Digital Input voltage  |                      |                    | -0.3         | VD+0.3     | V     |

| Ambient Temperature    | (Power Applied)      |                    | -55          | +125       | °C    |

| Storage Temperature    |                      |                    | -65          | +150       | °C    |

Warning: Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

# **RECOMMENDED OPERATING CONDITIONS** (AGND, DGND = 0V, all voltages with repect to 0V.)

| Parameter                     | Symbol         | Min  | Тур | Max  | Units |

|-------------------------------|----------------|------|-----|------|-------|

| Power Supplies: Digital       | VD1-VD4        | 4.75 | 5.0 | 5.25 | V     |

| Analog                        | VA1,VA2        | 4.75 | 5.0 | 5.25 | V     |

| Operating Ambient Temperature | T <sub>A</sub> | 0    | 25  | 70   | ů     |

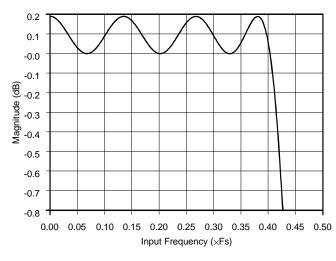

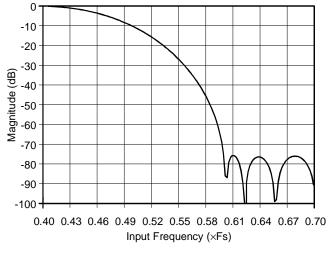

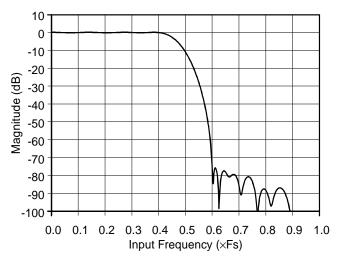

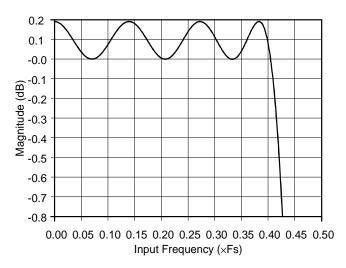

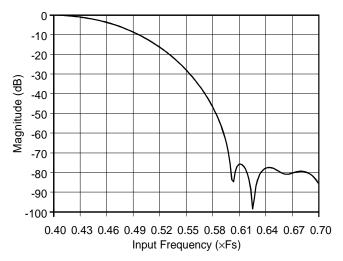

# **DIGITAL FILTER CHARACTERISTICS**

| Parameter                           |                                                                   | Symbol | Min     | Тур | Max                     | Units       |

|-------------------------------------|-------------------------------------------------------------------|--------|---------|-----|-------------------------|-------------|

| Passband                            |                                                                   |        | 0       |     | 0.40xFs                 | Hz          |

| Frequency Response                  |                                                                   |        | -0.5    |     | +0.2                    | dB          |

| Passband Ripple                     | (0-0.4xFs)                                                        |        |         |     | ±0.1                    | dB          |

| Transition Band                     |                                                                   |        | 0.40xFs |     | 0.60xFs                 | Hz          |

| Stop Band                           |                                                                   |        | 0.60xFs |     |                         | Hz          |

| Stop Band Rejection                 |                                                                   |        | 74      |     |                         | dB          |

| Group Delay                         | 16- and 8-bit formats<br>ADPCM stereo format<br>ADPCM mono format |        |         |     | 10/Fs<br>14/Fs<br>18/Fs | S<br>S<br>S |

| Group Delay Variation vs. Frequency | ADCs<br>DACs                                                      |        |         |     | 0.0<br>0.1/Fs           | μs<br>μs    |

# **DIGITAL CHARACTERISTICS** ( $T_A = 25$ °C; VA1, VA2, VD1-VD4 = 5V; AGND1, AGND2, DGND1-DGND4, DGND7, DGND8 = 0V.)

| Parameter                  |                      |                                                     |     | Min           | Max              | Units |

|----------------------------|----------------------|-----------------------------------------------------|-----|---------------|------------------|-------|

| High-level Input Voltage   | XTAL1                | Digital Inputs<br>I, XTAL2I, PDWN                   | ViH | 2.0<br>VD-1.0 | VD+0.3<br>VD+0.3 | V     |

| Low-level Input Voltage    |                      |                                                     | VIL | -0.3          | 0.8              | V     |

| High-level Output Voltage: | D<7:0><br>All Others | $I_0 = -16.0 \text{ mA}$<br>$I_0 = -1.0 \text{ mA}$ | Voн | 2.4<br>2.4    | VD<br>VD         | V     |

| Low-level Output Voltage:  | D<7:0><br>All Others | $I_0 = 16.0 \text{ mA}$<br>$I_0 = 4.0 \text{ mA}$   | VoL |               | 0.4<br>0.4       | V     |

| Input Leakage Current      |                      | (Digital Inputs)                                    |     | -10           | 10               | μΑ    |

| Output Leakage Current     | (High-               | Z Digital Outputs)                                  |     | -10           | 10               | μΑ    |

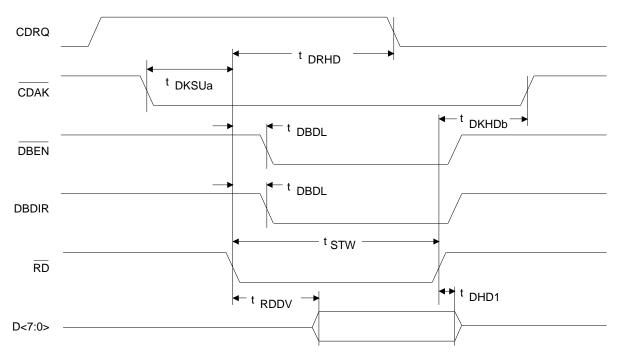

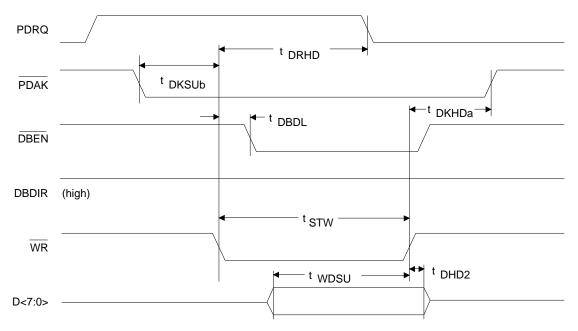

**TIMING PARAMETERS** ( $T_A = 25$  °C; VA1, VA2, VD1-VD4 = +5V, outputs loaded with 30 pF; Input Levels: Logic 0 = 0V, Logic 1 = VD1-VD4)

| Parameter                                                                                            | Symbol                                   | Min      | Max   | Units    |

|------------------------------------------------------------------------------------------------------|------------------------------------------|----------|-------|----------|

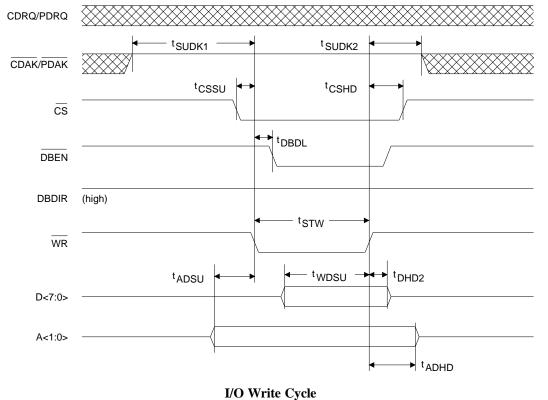

| WR or RD strobe width                                                                                | tstw                                     | 90       |       | ns       |

| Data valid to WR rising edge (write cycle)                                                           | twosu                                    | 22       |       | ns       |

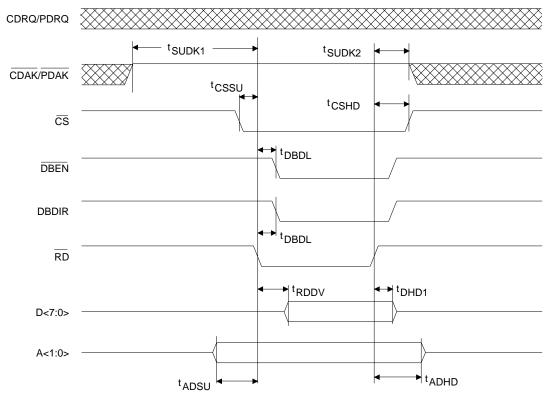

| RD falling edge to data valid (read cycle)                                                           | trddv                                    |          | 60    | ns       |

| CS setup to WR of RD falling edge                                                                    | tcssu                                    | 10       |       | ns       |

| CS hold from WR or RD rising edge                                                                    | tcshd                                    | 0        |       | ns       |

| ADDR <> setup to RD or WR falling edge                                                               | tadsu                                    | 22       |       | ns       |

| ADDR <> hold from WR or RD rising edge                                                               | tadhd                                    | 10       |       | ns       |

| DAK inactive to WR or RD falling edge (DMA cycle completion immediately followed by a non-DMA cycle) | tsudk1                                   | 60       |       | ns       |

| DAK active from WR or RD rising edge (non-DMA cycle completion immediately followed by DMA cycle)    | tsudk2                                   | 0        |       | ns       |

| DAK setup to RD falling edge (DMA cycles)                                                            | tDKSUa                                   | 25<br>25 |       | ns       |

| DAK setup to WR falling edge                                                                         | toksub                                   | 25<br>15 |       | ns       |

| Data hold from WR rising edge DRQ hold from WR or RD falling edge                                    | tDHD2                                    | 0        | 25    | ns       |

| (assumes no more DMA cycles needed)                                                                  | tDRHD                                    | U        | 25    | ns       |

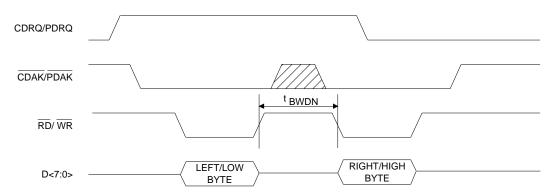

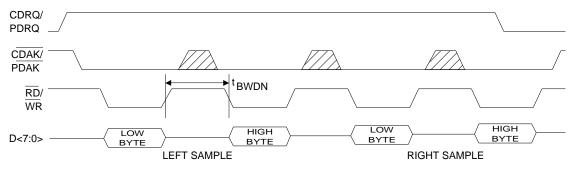

| Time between rising edge of WR or RD to next falling edge of WR or RD                                | t <sub>BWND</sub>                        | 80       |       | ns       |

| Data hold from RD rising edge                                                                        | t <sub>DHD1</sub>                        | 0        | 20    | ns       |

| DAK hold from WR rising edge DAK hold from RD rising edge                                            | t <sub>DKHDa</sub><br>t <sub>DKHDb</sub> | 25<br>25 |       | ns<br>ns |

| DBEN or DBDIR active from WR or RD falling edge                                                      | t <sub>DBDL</sub>                        |          | 40    | ns       |

| PDWN pulse width low                                                                                 | tpdwn                                    | 200      |       | ns       |

| Crystals, XTAL1I, XTAL2I frequency (Notes 1,7,8)                                                     |                                          |          | 25.6  | MHz      |

| XTAL1I, XTAL2I high time (Notes 1,8)                                                                 |                                          | 18       |       | ns       |

| XTAL1I, XTAL2I low time (Notes 1,8)                                                                  | 1                                        | 18       |       | ns       |

| Sample frequency (Note 1)                                                                            | Fs                                       | 5.5      | 50    | kHz      |

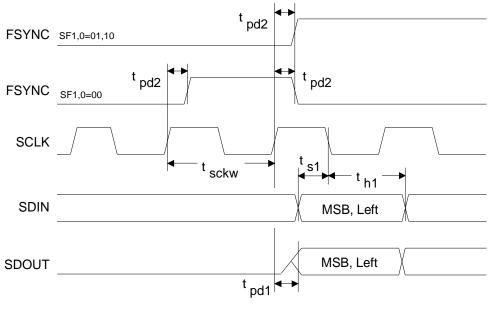

| Serial Port Timing                                                                                   |                                          |          |       |          |

| SCLK frequency (Note 9)                                                                              | tsclkw                                   |          | Fsx64 | Hz       |

| SCLK rising to SDOUT valid                                                                           | t <sub>PD1</sub>                         |          | 30    | ns       |

| SCLK rising to FSYNC transition                                                                      | t <sub>PD2</sub>                         | -20      | 20    | ns       |

| SDIN valid to SCLK falling                                                                           | t <sub>S1</sub>                          | 30       |       | ns       |

| SDIN hold after SCLK falling                                                                         | t <sub>H1</sub>                          | 30       |       | ns       |

- Notes: 7. When only one crystal is used, it must be XTAL1. When using two crystals, the high frequency crystal should be on XTAL1 which is designed for higher loop gains.

- 8. Sample frequency specifications must not be exceeded.

- 9. When SF1, 0 = 10, 32-bit mode, SCLK is active for the first 32 bit periods of the frame, and remains low during the last 32 bit periods of the frame.

**Serial Port Timing**

8-Bit Mono DMA Read/Capture Cycle

8-Bit Mono DMA Write/Playback Cycle

8-Bit Stereo or 16-Bit Mono DMA Cycle

16-Bit Stereo or ADPCM DMA Cycle

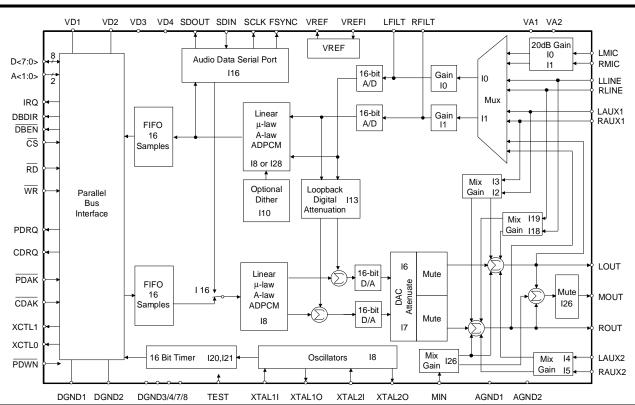

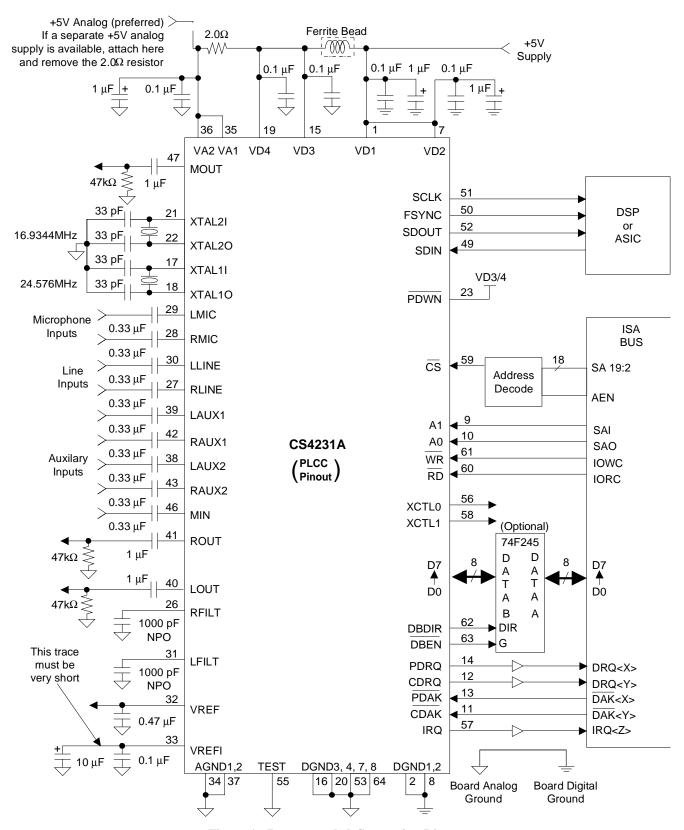

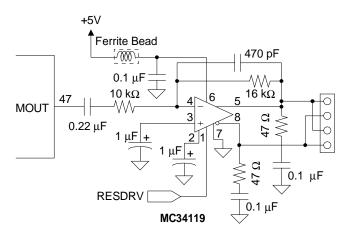

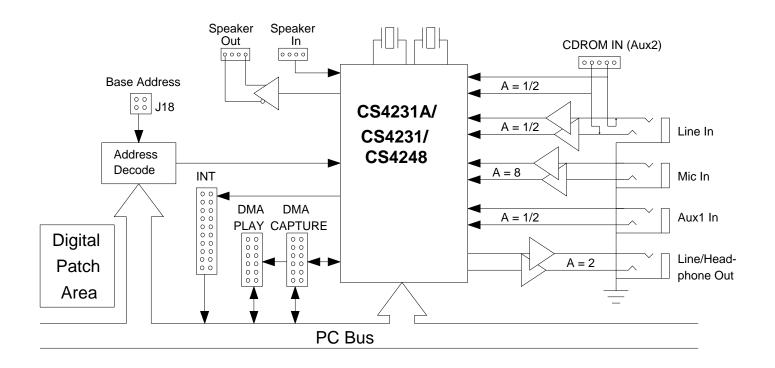

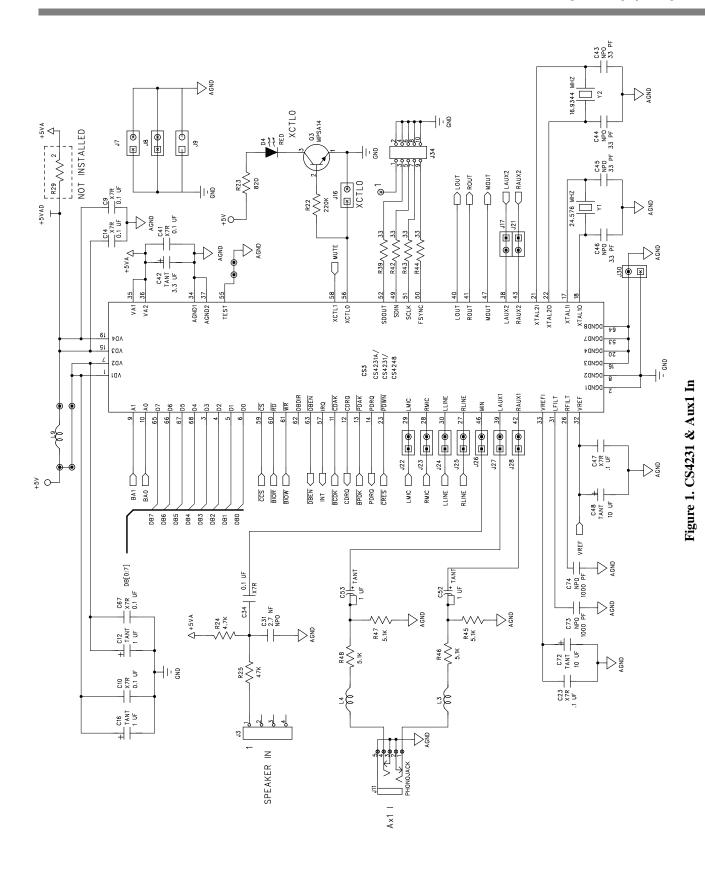

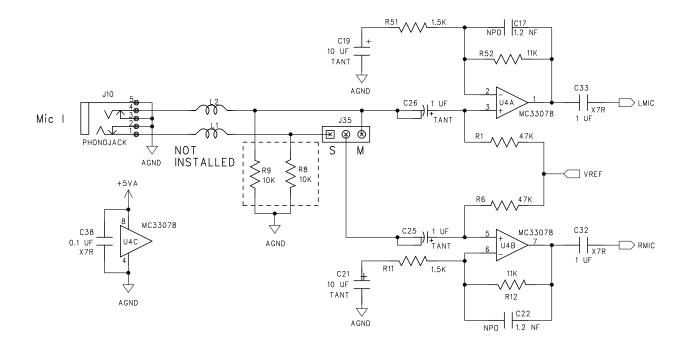

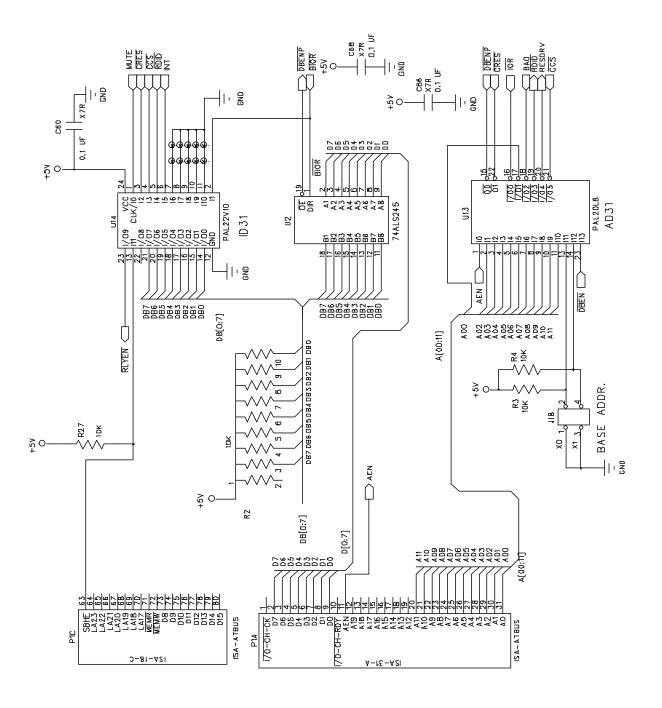

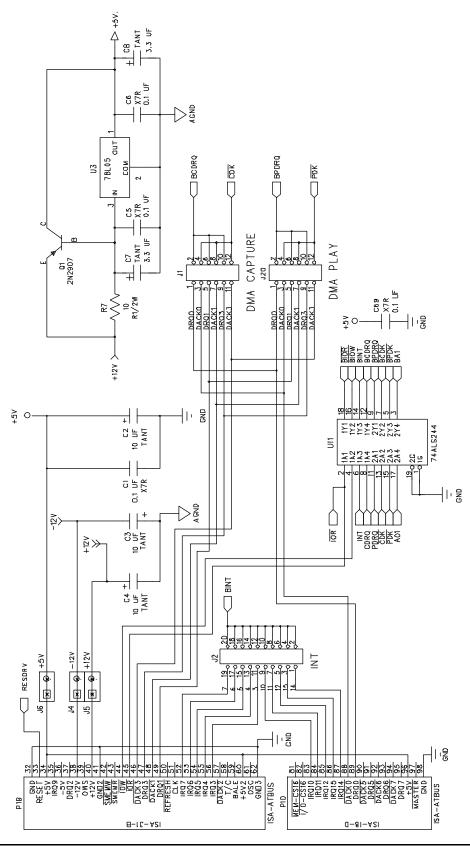

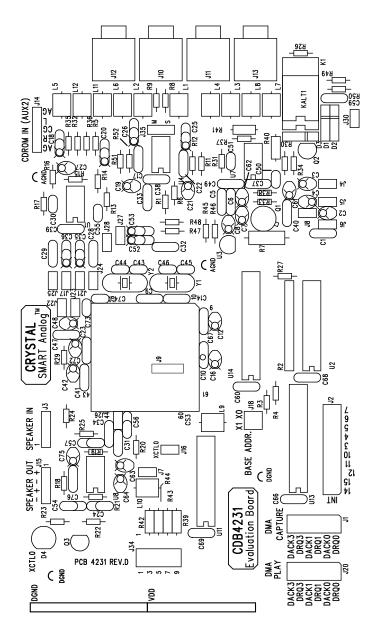

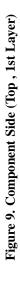

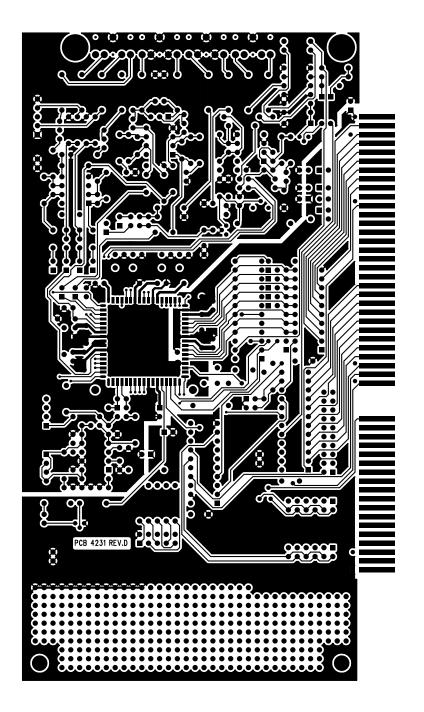

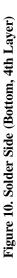

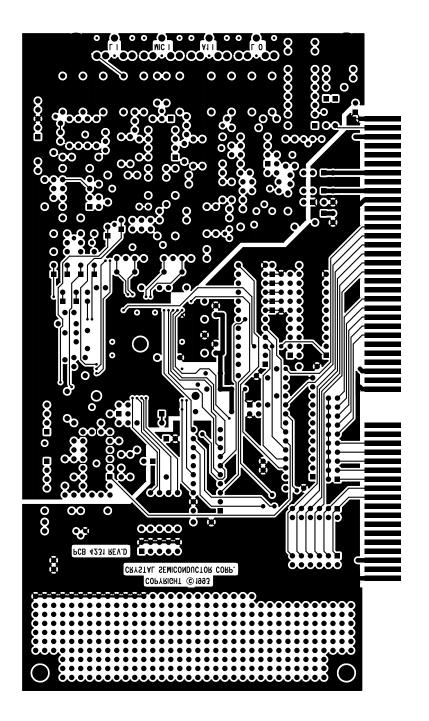

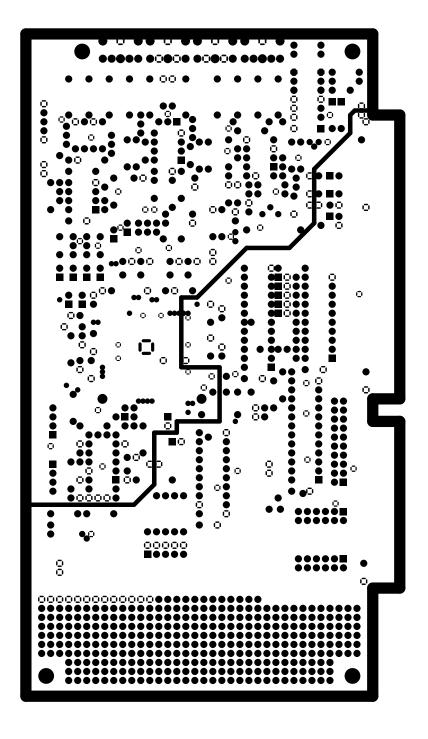

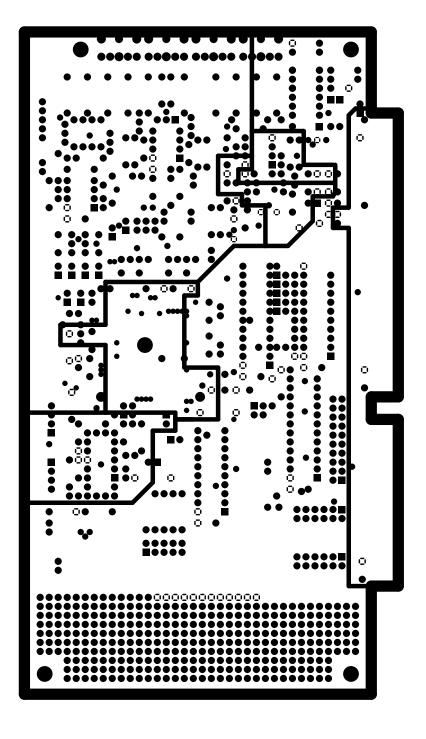

Figure 1. Recommended Connection Diagram (See Figures 16 & 17 for Layout Recommendations)

#### GENERAL DESCRIPTION

The CS4231A is a monolithic integrated circuit that provides audio in personal computers or other parallel interface environments. The functions include stereo Analog-to-Digital and Digital-to-Analog converters (ADCs and DACs), analog mixing, anti-aliasing and reconstruction filters, line and microphone level inputs, optional A-Law / μ-Law coding, simultaneous capture and playback and a parallel bus interface. Five analog inputs are provided and three can be multiplexed to the ADC. The line input, two auxiliary inputs and a mono input can be mixed with the output of the DAC with full volume control. Several data modes are supported including 8- and 16-bit linear as well as 8-bit companded, 4-bit ADPCM compressed, and 16bit Big Endian. The CS4231A is packaged in a 68-pin PLCC or a 100-pin TQFP.

# **Enhanced Functions (MODE 2)**

The CS4231A's initial state is labeled MODE 1 and forces the CS4231A to appear as a CS4248. Enhanced functionality is provided by a second mode on the CS4231A. To switch from MODE 1 to MODE 2, the MODE2 bit should be set to one in the MODE and ID register (I12). When MODE 2 is selected, the bit IA4 in the Index Address register (R0) will be decoded as a valid index pointer, providing 16 additional registers and increased functionality over the CS4248.

To reverse the procedure, clear the MODE2 bit and the CS4231A will resume operation in MODE 1. Since previous code writes a zero to bit IA4 of the Index Address register (R0), the CS4231A is backwards compatible with the CS4248 and the AD1848.

# Mixer Attenuation Control on Line Input

The CS4231A adds mixer attenuation control for the LINE inputs which are then summed into the output mixer. This fourth input to the mixer completes the recommended mixer configuration for MPC Level-2 compliance. The LINE mix register provides 32 volume adjustments in 1.5 dB steps. In addition, there is a one bit mute control.

The additional MODE 2 functions are:

- 1. Full-Duplex DMA support

- 2. A programmable timer

- 3. Mono output with mute control

- 4. Mono input with mixer volume control

- 5. ADPCM and Big Endian audio data formats

- 6. Independent selection of capture and playback audio data formats

- 7. Selectable serial audio data port.

#### ANALOG HARDWARE DESCRIPTION

The analog hardware consists of an MPC Level 2-compatible mixer (four stereo mix sources), three line-level stereo inputs, a stereo microphone input, a mono input, a mono output, and a stereo line output. This section describes the analog hardware needed to interface with these pins.

# **Analog Inputs**

The analog inputs consist of four stereo analog inputs, and one mono input. As shown on this data sheet cover, the input to the ADCs comes from a multiplexer that selects between two analog line-level inputs (LINE, AUX1), a microphone level input (MIC), and the output from the MPC-compatible mixer. The LINE and AUX1 lines also feed the MPC mixer and include individual volume controls. Unused analog inputs should be connected together and then connected through a capacitor to analog ground.

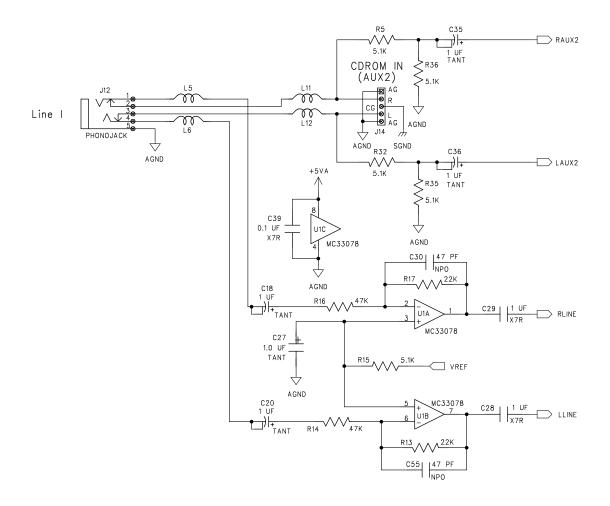

#### Line-Level Inputs plus MPC Mixer

The analog input interface is designed to accommodate four stereo inputs and one mono input. Three of these sources are multiplexed to the ADC. These inputs are: a stereo line-level input (LINE), a stereo microphone input (MIC), and a stereo auxiliary line-level input (AUX1). The LINE and AUX1 inputs have a separate path, with volume control, to the output analog mixer which has the additional inputs of a stereo AUX2 channel, a mono input channel, and the output of the DACs. All audio inputs should be capacitively coupled to the CS4231A.

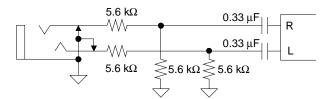

Since some analog inputs can be as large as 2 V<sub>RMS</sub>, the circuit shown in Figure 2 can be used to attenuate the analog input to 1 V<sub>RMS</sub> which is the maximum voltage allowed for the line-level inputs on the CS4231A.

Figure 2. Line Inputs

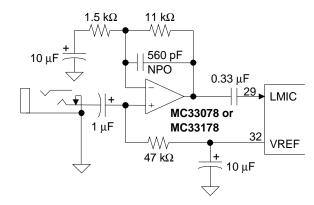

# Microphone Level Inputs

The microphone level inputs, LMIC and RMIC, include a selectable + 20dB gain stage for interfacing to an external microphone. The 20 dB gain block can be turned off to provide another stereo line-level input. Figure 3 illustrates a single-ended microphone input buffer with +18 dB of gain that will support lower gain mics, and should be placed as close to the input jack as possible to minimize noise coupling.

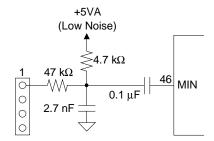

#### Mono Input with Attenuation and Mute

The mono input, MIN, is useful for mixing the output of the "beeper" (timer chip), provided in

Figure 3. Left or Mono Microphone Input

all PCs, with the rest of the audio signals. The attenuation control allows 16 levels in -3dB steps. In addition, a mute control is provided. The attenuator is a single channel block with the resulting signal sent to the output mixer where it is mixed with the left and right outputs. Figure 4 illustrates a typical input circuit for the Mono In. Although this input is described for a low-quality beeper, the input is of the same high-quality as all other analog inputs and may be used for other purposes. At power-up, the MIN line is unmuted (as is the mono out line) allowing the initial beeps heard, when the computer is initializing, to pass through.

Figure 4. Mono Input

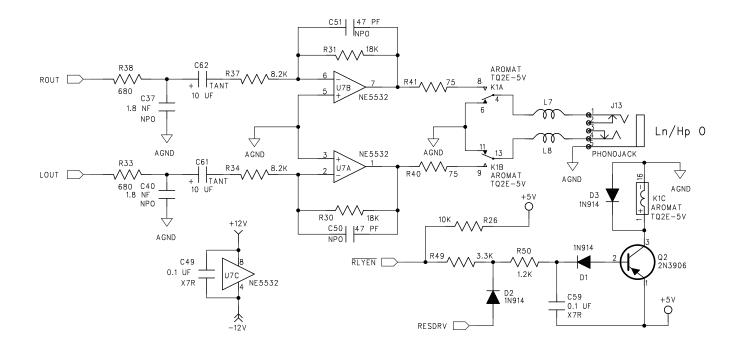

# **Analog Outputs**

The analog output section of the CS4231A provides a stereo line-level output. The other output types (headphone and speaker) can be implemented with external circuitry. LOUT and ROUT outputs should be capacitively coupled to external circuitry.

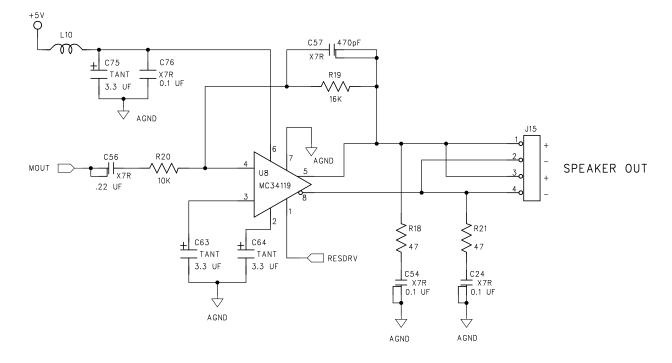

#### Mono Output with Mute Control

The mono output, MOUT, is a sum of the left and right output channels, attenuated by 6dB to prevent clipping at full scale. The mono out channel can be used to drive the PC-internal mono speaker using an appropriate drive circuit. This approach allows the traditional PC-sounds to be integrated with the rest of the audio system. Figure 5 illustrates a typical speaker driver circuit. The mute control is independent of the line outputs allowing the mono channel to mute the speaker without muting the line outputs. The power-up default has MIN and MOUT enabled to provide a pass-through for the beeps heard at power-up.

Figure 5. Mono Output

# Miscellaneous Analog Signals

The LFILT and RFILT pins must have a 1000 pF NPO capacitor to analog ground. These capacitors, along with an internal resistor, provide a single-pole low-pass filter used at the inputs to the ADCs. By placing these filters at the ADC inputs, low-pass filters at each analog input pin are avoided.

The VREFI pin is used to lower the noise of the internal voltage reference. A 10µF and 0.1µF capacitor to analog ground should be connected with a short wide trace to this pin. No other connection should be made, since noise coupling

onto this pin can degrade the analog performance of the codec. Likewise, digital signals should be kept away from VREFI for similar reasons.

The VREF pin is typically 2.1 V and provides a common mode signal for single-supply external circuits. VREF only supports DC loads and should be buffered if AC loading is needed. For typical use, a 0.47  $\mu$ F capacitor should be connected to VREF. The signal-to-noise ratio of the microphone inputs can be improved by increasing the capacitance on VREF to 10  $\mu$ F.

#### DIGITAL HARDWARE DESCRIPTION

The digital hardware consist of the data bus, address bus, and control signals needed for the parallel bus, as well as an interrupt and DMA signals.

# Parallel Data Interface

The 8-bit parallel port of the CS4231A provides an interface which is compatible with most computer peripheral busses. This parallel interface is designed to operate on the Industry Standard Architecture (ISA) bus, but the CS4231A will easily interface with other buses such as EISA and Microchannel. Two types of accesses can occur via the parallel interface: Programmed I/O (PIO) access, and DMA access.

There is no provision for the CS4231A to "hold off" or extend a cycle occurring on the parallel interface. Therefore, the internal architecture of the CS4231A accepts asynchronous parallel bus cycles without interfering with the flow of data to or from the ADC and DAC sections.

#### **FIFOs**

The CS4231A contains 16-sample FIFOs in both the playback and capture paths. The FIFOs are

transparent and have no programming associated with them.

When playback is enabled, the playback FIFO continually requests data until the FIFO is full, and then makes requests as positions inside the FIFO are emptied, thereby keeping the playback FIFO as full as possible. Thus when the system cannot respond within a sample period, the FIFO is emptied, avoiding a momentary loss of audio data. If the FIFO runs out of data, the last valid sample can be continuously output to the DACs (if DACZ in I16 is set) which will eliminate pops from occurring.

When capture is enabled, the capture FIFO tries to continually stay empty by making requests every sample period. Thus when the system cannot respond within a sample period, the capture FIFO starts filling thereby avoiding a loss of data in the audio data stream.

# High Current Data Bus Drivers

The CS4231A provides 16 mA drivers eliminating the need for off chip drivers in many cases. If a full 24 mA drive is required, the appropriate direction and driver select lines are provided. The current drivers are provided for the data bus, DMA request line, and the interrupt request line.

# PIO Registers Interface

The first type of parallel bus access is programmed I/O (PIO) to the four control registers. The control registers allow access to status, audio data, and all indirect registers via the index registers. The RD and WR signals are used to define the read and write cycles respectively. The PIO register cycle is defined by the assertion of the CS4231A CS signal while the DMA acknowledge signals, CDAK and PDAK, are inactive. For read cycles, the CS4231A will drive data on the DATA lines while the host asserts the RD strobe. Write cycles require the host to assert data on the DATA lines and strobe the WR signals.

nal. The CS4231A will latch data into the PIO register on the rising edge of the WR strobe. The CS4231A CS signal should remain active until after completion of the read or write cycle. I/O cycles are the only type of cycle which can access the internal control and status registers.

When reading or writing audio data via PIO, the Status register (R2) indicates which byte of the audio sample is ready. The Status register does not have to be read after every byte; however, once all bytes of a sample are transferred, the Status register must be read before the next sample can be transferred.

The audio data interface typically uses DMA request/grant pins to transfer the digital audio data between the CS4231A and the bus. The CS4231A is responsible for asserting a request signal whenever the CS4231A's internal buffers need updating. The logic interfaced with the CS4231A responds with an acknowledge signal and strobes data to and from the CS4231A, 8 bits at a time. The CS4231A keeps the request pin active until the appropriate number of 8-bit cycles have occurred to transfer one audio sample. Notice that different audio data types will require a different number of 8-bit transfers.

# DMA Interface

The second type of parallel bus cycle on the CS4231A is a DMA transfer. DMA cycles are distinguished from PIO register cycles by the assertion by the CS4231A of a CDRQ (or PDRQ) followed by an acknowledgment by the host by the assertion of CDAK (or PDAK). While the acknowledgment is received from the host, the CS4231A assumes that any cycles occurring are DMA cycles and ignores the addresses on the address lines and the CS line.

The CS4231A may assert the DMA request signal at any time. Once asserted, the DMA request will remain asserted until a DMA cycle occurs to the CS4231A. Once the falling edge of the final

WR or RD strobe of a full sample of a DMA cycle occurs, the DMA request signal is negated immediately. DMA transfers may be terminated by resetting the PEN and/or CEN bits in the Interface Configuration register (I9), depending on the DMA that is in progress (playback, capture, or both). Termination of DMA transfers may only happen between sample transfers on the bus. If PDRQ and/or CDRQ goes active while resetting PEN and/or CEN, the request must be acknowledged (PDAK and/or CDAK) and a final sample transfer completed. The CS4231A supports up to two DMA channels.

#### Dual DMA Channel Mode

In dual DMA channel mode, playback and capture DMA requests and acknowledges occur on independent DMA channels. In this mode, capture and playback are enabled and set for DMA transfers. In addition, the dual DMA mode must be set (SDC = 0). The Playback- and Capture-Enables (PEN, CEN, I9) can be changed without a Mode Change Enable (MCE, R0). This allows for proper full duplex control where applications are independently using playback and capture.

# Single DMA Channel (SDC) Mode

When two DMA channels are not available, the SDC mode forces all DMA transfers (capture or playback) to occur on a single DMA channel (playback channel). The trade-off is that the CS4231A will no longer be able to perform simultaneous DMA capture and playback.

To enable the SDC mode, set the SDC bit in the Interface Configuration register (I9). With the SDC bit asserted, the internal workings of the CS4231A remain exactly the same as dual mode, except for the manner in which DMA request and acknowledges are handled.

The playback of audio data will occur on the playback channel exactly as dual channel operation. However, the capture audio channel is now diverted to the playback channel. This means that the capture <u>DMA</u> request occurs on the PDRQ pin and the <u>PDAK</u> pin is used to acknowledge the capture request. (In MODE 2, the capture data format is always set in register I28.) Note, simultaneous capture and playback cannot occur in SDC mode. If both playback and capture are enabled, the default will be playback.

In SDC mode, the CDRQ pin is logic low (inactive). The CDAK pin is ignored by the CS4231A. SDC does not have any affect when using PIO accesses.

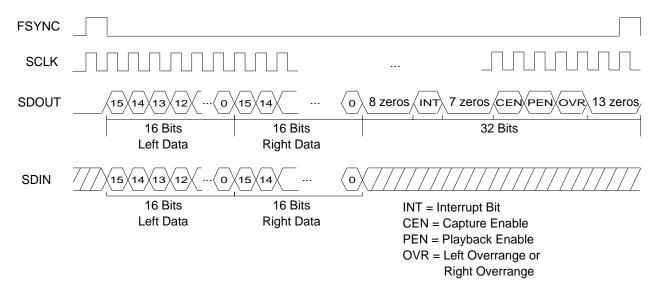

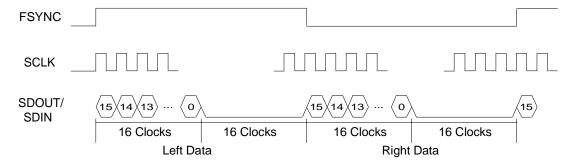

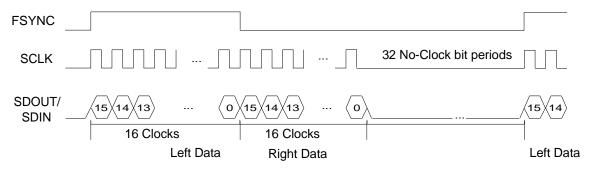

#### Serial Audio Data Port

The bits controlling the serial port can only be changed when the Mode Change Enable bit, MCE, in R0 is high. The audio serial port is software selectable via the SPE bit in I16. Once enabled, the data from the ADCs is sent to the SDOUT pin and the audio data input on the SDIN pin is routed to the DACs. The parallel bus on the CS4231A is still used for control information such as volume and audio data formats. While the serial port is enabled, audio data can still be read from the codec ADCs (capture) on the parallel port, but the DACs (playback) only accept data from the serial port in pin. When the serial port is disabled (SPE = 0); FSYNC, SCLK, and SDOUT are held low.

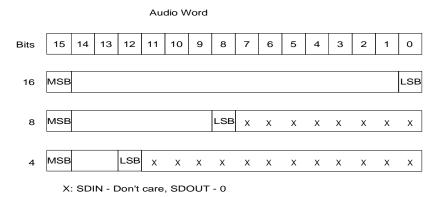

FSYNC and SCLK are always output from the CS4231A. The serial port can be configured in one of three serial port formats, shown in Figures 6-8. SF1 and SF0 in I16 select the particular format. Both left and right audio words are always 16 bits wide with the actual audio data left justified in the word (i.e. ADPCM occupies the first four bits). Unused bits are output as zeros after the LSB. The justification is illustrated in Figure 9. When the mono audio format is selected, the right channel output is set to zero and the left channel input is sent to both DAC channels. When changing sample frequencies the

output clocks will stretch, but will not have any glitches. This allows the serial port to operate through a sample frequency change.

The first format - SPF0, shown in Figure 6, is called 64-bit enhanced. This format has 64 SCLKs per frame with a one bit period wide FSYNC that precedes the frame. The first 16 bits

Figure 6. 64-bit enhanced mode (SF1,0 = 00)

Figure 7. 64-bit mode (SF1,0 = 01)

Figure 8. 32-bit mode (SF1,0 = 10)

is the left word and the second 16 bits is the right word. The last 32 bits contains four status bits and 28 zeros. This is the only mode that contains status information.

The second serial format - SPF1, shown in Figure 7, is called 64-bit mode. This format also has 64 SCLKs per frame, but has FSYNC transitioning high at the start of the left data word and transitioning low at the start of the right data word. Both the left and the right data word are followed by 16 zeros.

The third serial format - SPF2, shown in Figure 7, is called 32-bit mode. This format contains 32 SCLKs per frame wherein FSYNC is high for the left channel and low for the right channel. The absolute time is similar to the other two modes but SCLK is stopped after the right channel is finished until the start of the next frame (stopped for 32 bit period times). This mode is useful for DSPs that do not want the interrupt overhead of the 32 unused bit periods. As an example, if a DSP serial word length is 16 bits, then four interrupts will occur in SPF0 and SPF1; whereas in SPF2 the DSP will only get two interrupts.

# Miscellaneous Signals

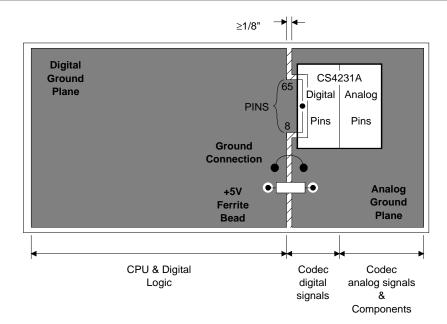

The power supply providing analog power should be as clean as possible to minimize noise coupling into the analog section and degrading analog performance. The VD1 and VD2 pins are isolated from the rest of the digital power pins and provide digital power for the asynchronous parallel bus. These two pins can be connected directly to the digital power supply. VD3 and VD4 digital power supply pins provide power to the internal digital section of the codec and should be optimally quieter than VD1 and VD2. This can be achieved by using a ferrite bead as shown in the typical connection diagram in Figure 1. Grounding is covered in the *Grounding and Layout* section.

An interrupt pin, IRQ, is provided to allow for host notification by the CS4231A. Since the interrupt is mainly a software function, it is described in more detail under the software section.

# Crystals / Clocks

Four pins have been allocated to allow the interfacing of two crystal oscillators to the CS4231A: XTAL1I, XTAL1O, XTAL2I, XTAL2O. The crystals should be designed as fundamental mode, parallel resonant, with a load capacitor of between 10 and 20 pF. The capacitors shown in Figure 1, connected to each of the crystal pins, should be twice the load capacitance specified to the crystal manufacturer. The XTAL1 oscillator is designed with slightly more gain to handle

Figure 9. Serial Audio Data Justification

higher frequencies, but any crystal with the above specifications should suffice. The standard crystals for audio are:

XTAL1: 24.576 MHz

Fundamental Mode

Parallel Resonant,  $C_L = 20 pF$

XTAL2: 16.9344 MHz

Fundamental Mode

Parallel Resonant, C<sub>L</sub> = 20 pF

These crystal frequencies support the standard sample frequencies listed in Table 7.

External CMOS clocks may be connected the crystal inputs (XTAL1I, XTAL2I) in lieu of the crystals. When using external CMOS clocks, the XTAL out pins should be left floating. Extreme care should be used when laying out a board using external clocks since coupling between clocks can degrade analog performance.

# Power Down - PDWN

The PDWN signal places the CS4231A into maximum power conservation mode. When PDWN goes low, any reads of the codec's parallel interface return 80 hex, all analog outputs are muted, and the voltage reference then slowly decays to ground. When PDWN is brought high, a full calibration cycle automatically occurs. While the codec is initializing, any reads from the parallel interface will return 80 hex and writes will be ignored. When initialization is completed, the registers will contain their reset value as stated in the register section of the data sheet. The CS4231A contains an internal "Power On Reset" signal that causes a proper initialization at power up time. Therefore, if no power down mode is needed, PDWN can be tied permanently to VD3/4.

#### DBEN/DBDIR

If needed, the DBEN and DBDIR pins can control an external data buffer to the CS4231A. The CS4231A contains 16 mA bus drivers so the external data buffer is only needed when driving a full 24 mA bus. DBEN enables the external drivers and DBDIR controls the direction of the data flow. Both signals are normally high, where DBDIR high points the transceiver towards the codec and low points the transceiver towards the data bus. See Figure 1 for a typical connection diagram.

#### SOFTWARE DESCRIPTION

The CS4231A must be in Mode Change Enable Mode (MCE=1) before any changes to the Interface Configuration register (I9), the Sample Frequency (lower four bits) in the Fs & Playback Data Format register (I8), or the serial port bits (SF1, SF0, SPE) in the Alternate Feature Enable I register (I16) are allowed. The actual audio data formats, which are the upper four bits of I8 for playback and I28 for capture, can be changed by setting MCE (R0) or PMCE/CMCE (I16) high. The exceptions are CEN and PEN which can be changed "on-the-fly" via programmed I/O writes to these bits. All outstanding DMA transfers must be completed before new values of CEN or PEN are recognized.

#### Power-Down and Initialization

To put the CS4231A into a power-down mode, the PDWN pin is pulled low. In this state the host interface reads 80h indicating that it is unable to respond and all analog circuits are turned off.

To let the  $\overline{CS4231A}$  go through its reset initialization the  $\overline{PDWN}$  pin should be set high. This

rising edge starts the initialization process in which a full calibration occurs. While the CS4231A is initializing, 80 hex is returned from all reads by the host computer. All writes during initialization of the CS4231A will be ignored. At the end of the initialization, all registers are set to known reset values as documented in the register definition section.

#### Calibration Modes

The CS4231A has four different calibration modes. The selected calibration occurs whenever the Mode Change Enable (MCE, R0) bit goes from 1 to 0.

The completion of calibration can be determined by polling the Auto-Calibrate In-Progress bit in the Error Status and Initialization register (ACI, I11). This bit will be high while the calibration is in progress and low once completed. The calibration time varies with calibration mode.

The Calibration procedure is as follows:

- 1) Place the CS4231A in Mode Change Enable using the MCE bit of the Index Address register (R0).

- 2) Set the CAL1,0 bits in the Interface Configuration register (I9).

- 3) Return from Mode Change Enable by resetting the MCE bit of the Index Address register (R0).

- 4) Wait until ACI (I11) cleared to proceed

*No Calibration (CAL1,0 = 00)*

This is the fastest mode since no calibration is performed. This mode is useful for games which need to change the sample frequency quickly. This mode is also useful when the codec is operating in full-duplex and an ADC data format change is desired. This is the only calibration mode that does not affect the DACs (i.e. mute

the DACs at some point). Changing from any other calibration mode to No Calibration mode will take 40 sample periods to complete; however, subsequent MCE cycles will take 0 sample periods.

Converter Calibration (CAL1,0 = 01)

This calibration mode calibrates the ADCs and DACs but does not calibrate any of the analog mixing channels. This is the second longest calibration mode, taking 136 sample periods, and is software and hardware similar to the CS4231 or CS4248. Since the mixer is not calibrated, any analog signals mixing into the output will be unaffected. The calibration sequence done by the CS4231A is as follows:

The DACs are muted The ADCs are calibrated The DACs are calibrated The DACs are unmuted

DAC Calibration (CAL1,0 = 10)

This calibration mode only calibrates the DACs' (playback) interpolation filters leaving the ADCs unaffected. This is the second fastest calibration mode (no cal. is the fastest) taking 40 sample periods to complete. The calibration sequence done by the CS4231A is as follows:

The DACs are muted

The DAC filters are calibrated

The DACs are unmuted

Full Calibration (CAL1,0 = 11)

This calibration mode calibrates all offsets, ADCs, DACs, and analog mixers. Full calibration is automatically initiated on power up or anytime the CS4231A exits from a power down state. This is the longest calibration mode and takes 168 sample periods to complete. The calibration sequence done by the CS4231A is as follows:

All outputs are muted (DACs and mixer)

The mixer is calibrated

The ADCs are calibrated

The DACs are calibrated

All outputs are unmuted

# **Changing Sampling Rate**

The internal states of the CS4231A are synchronized by the selected sampling frequency defined in the Fs and Playback Data Format register (I8). The changing of either the clock source or the clock frequency divide requires a special sequence for proper CS4231A operation:

- 1) Place the CS4231A in Mode Change Enable using the MCE bit of the Index Address register (R0).

- 2) During a single write cycle, change the Clock Frequency Divide Select (CFS) and/or Clock 2 Source Select (C2SL) bits of the Fs & Playback Data Format register (I8) to the desired value. (The data format may also be changed.)

- 3) The CS4231A resynchronizes its internal states to the new clock. During this time the CS4231A will be unable to respond at its parallel interface. Writes to the CS4231A will not be recognized and reads will always return the value 80 hex.

- 4) The host now polls the CS4231A's Index Address register (R0) until the value 80 hex is no longer returned.

- 5) Once the CS4231A is no longer responding to reads with a value of 80 hex, normal operation can resume and the CS4231A can be removed from MCE.

The CSL and CFS bits cannot be changed unless the MCE bit has been set. Attempts to change the Data Format registers (I8, I28) or Interface Configuration register (I9, except CEN and PEN) without MCE set, will not be recognized. When fast changing of sample frequency is desired, the XTALE bit (I17) should be set. When set, both crystals are kept running thereby providing the fastest switching time (80h never appears) between sample frequencies. When XTALE is cleared, the unused crystal is powered down to minimize noise coupling. This causes 80h to appear after leaving an MCE cycle until the newly selected crystal is operational. XTALE (and the No Calibration mode, I9) provide the fastest switching time for applications such as games that constantly change the sample frequency.

# Changing Audio Data Formats

In MODE 1, MCE must be used to select the audio data format in I8. Since MCE causes a calibration cycle, it is not ideal for full-duplex operation. In MODE 2, individual Mode Change Enable bits for capture and playback are provided in register I16. MCE (R0) must still be used to select the sample frequency, but PMCE (for playback) and CMCE (for capture) allow changing their respective data formats without causing a calibration to occur. Setting PMCE (I16) clears the playback FIFO and allows the upper four bits of I8 to be changed. Setting CMCE (I16) clears the capture FIFO and allows the upper four bits of I28 to be changed.

#### Audio Data Formats

In MODE 1 operation, all data formats of the CS4231A are in "little endian" format. This format defines the byte ordering of a multibyte word as having the least significant byte occupying the lowest memory address. Likewise, the most significant byte of a little endian word occupies the highest memory address.

The sample frequency is always selected in the Fs and Playback Data Format register (I8). In MODE 1 the same register, I8, determines the audio data format for both playback and capture; however, in MODE 2, I8 only selects the play-

back data format and the capture data format is independently selectable in the Capture Data Format register (I28).

The CS4231A always orders the left channel data before the right channel. Note that these definitions apply regardless of the specific format of the data. For example, 8-bit linear data streams look exactly like 8-bit companded data streams. Also, the left sample always comes first in the data stream regardless of whether the sample is 16- or 8-bit in size.

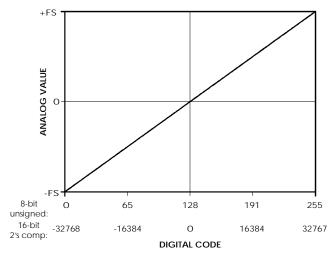

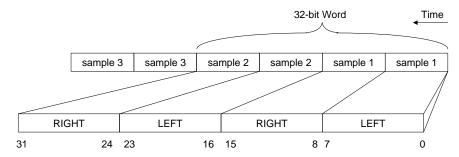

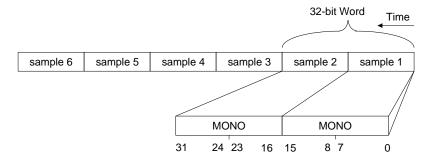

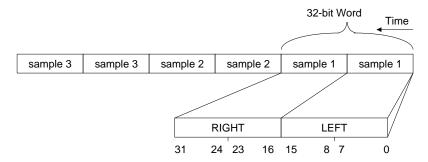

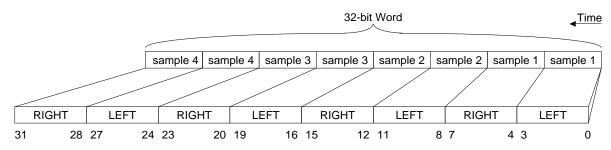

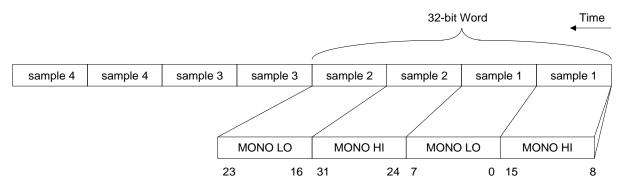

There are four data formats supported by the CS4231A during MODE 1 operation: 16-bit signed (little endian), 8-bit unsigned, 8-bit companded  $\mu$ -Law, and 8-bit companded A-Law. See Figures 12 through 15.

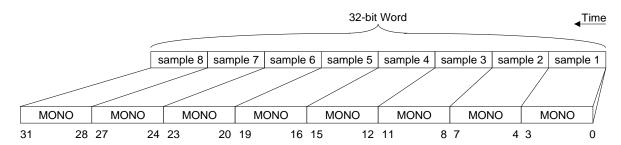

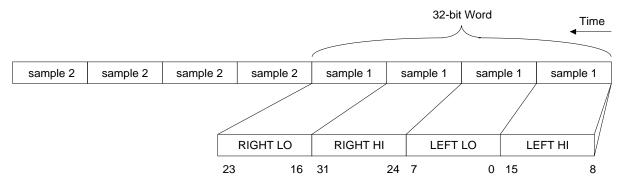

Additional data formats are supported in MODE 2 operation: 4-bit ADPCM, and 16-bit signed big endian. See Figures 16 through 19. With the addition of the Big Endian and ADPCM audio data formats, the CS4231A is compliant with the IMA recommendations for digital audio data formats (and sample frequencies).

Figure 10. Linear Transfer Functions

#### 16-bit Signed

The 16-bit signed format (also called 16-bit 2's complement) is the standard method of representing 16-bit digital audio. This format gives 96 dB theoretical dynamic range and is the standard for compact disk audio players. This format uses the value -32768 (8000h) to represent maximum negative analog amplitude while 32767 (7FFFh) represents maximum positive analog amplitude.

# 8-bit Unsigned

The 8-bit unsigned format is commonly used in the personal computer industry. This format delivers a theoretical dynamic range of 48 dB. This format uses the value 0 (00h) to represent maximum negative analog amplitude while 255 (FFh) represents maximum positive analog amplitude. The 16-bit signed and 8-bit unsigned transfer functions are shown in Figure 10.

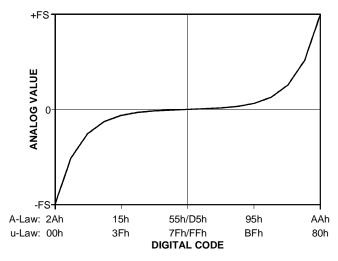

# 8-bit Companded

The 8-bit companded formats (A-Law and  $\mu$ -Law) come from the telephone industry.  $\mu$ -Law is the standard for the United States/Japan while A-Law is used in Europe. Companded audio allows either 64 dB or 72 dB of dynamic range

Figure 11. Companded Transfer Functions

Figure 12. 8-bit Mono, Unsigned Audio Data

Figure 13. 8-bit Stereo, Unsigned Audio Data

Figure 14. 16-bit Mono, Signed Little Endian Audio Data

Figure 15. 16-bit Stereo, Signed Little Endian Audio Data

Figure 16. 4-bit Mono, ADPCM Audio Data

Figure 17. 4-bit Stereo, ADPCM Audio Data

Figure 18. 16-bit Mono, Signed Big Endian Audio Data

Figure 19. 16-bit Stereo, Signed Big Endian Audio Data

using only 8-bits per sample. This is accomplished using a non-linear companding transfer function which assigns more digitalization codes to lower amplitude analog signals with the sacrifice of precision on higher amplitude signals. The  $\mu$ -Law and A-Law formats of the CS4231A conform to the CCITT G.711 specifications. Figure 11 illustrates the transfer function for both A-and  $\mu$ -Law. Please refer to the standards mentioned above for an exact definition.

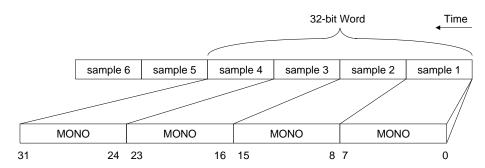

# ADPCM Compression/Decompression

In MODE 2, the CS4231A also contains Adaptive Differential Pulse Code Modulation (ADPCM) for improved performance and compression ratios over μ-Law or A-Law. The ADPCM format is compliant with the IMA standard and provides a 4-to-1 compression ratio (i.e. 4 bits are saved for each 16-bit sample captured). For more detailed information on the IMA ADPCM format contact the IMA at (410) 626-1380. Figures 16 and 17 illustrate the ADPCM data flow.

The ADPCM format is unique with respect to the FIFO depth and the DMA Base register value. The ADPCM format fills the FIFOs completely (64 bytes); therefore, the FIFOs hold 64 stereo samples and 128 mono samples. When samples are transferred using DMA, the DMA request stays active for four bytes, similar to the 16-bit stereo mode. The Status register indicates which of the four bytes is being transferred in PIO mode.

When CEN is 0 (capture disabled), the ADPCM block's accumulator and step size are cleared. When CEN is enabled, the ADPCM block will start converting. The "overrun" condition should never occur, otherwise the data may not be constructed properly upon playback. If pausing the capture sequence is desired, the ADPCM Capture Freeze bit (ACF, I23) should be set. When set, the ADPCM algorithm will continue to oper-

ate until a complete word (4 bytes) is written to the FIFO. Then the ADPCM's block accumulator and step size will be frozen. The user is required to read the FIFO until empty, at which time the requests will stop. When ACF is cleared, the ADPCM adaptation will continue.

When PEN is 0 (playback disabled), the ADPCM block's accumulator and step size are cleared. When PEN is set, the ADPCM block will start converting. When pausing the playback stream is desired, audio data should not be sent to the codec causing an underrun. This can be accomplished by disabling the DMA controller or not sending data in PIO mode. The underrun will be detected by the CS4231A and the adaptation will freeze. As data is sent to the codec, adaptation is resumed. It is critical that all playback ADPCM samples are sent to the codec, since dropped samples will cause errors in the adaptation. Whereas toggling PEN resets the accumulator and step size, the APAR bit (I17) only resets the accumulator without affecting the step size.

#### **DMA Registers**

The DMA registers allow easier integration of the CS4231A in ISA systems. Peculiarities of the ISA DMA controller require an external count mechanism to notify the host CPU of a full DMA buffer via interrupt. The programmable DMA Base registers provide this service.

The act of writing a value to the Upper Base register causes both Base registers to load the Current Count register. DMA transfers are enabled by setting the PEN/CEN bit while PPIO/CPIO is clear. (PPIO/CPIO can only be changed while the MCE bit is set.) Once transfers are enabled, each sample that is transferred by a DMA cycle will decrement the appropriate Current Count register (with the exception of the ADPCM format) until zero is reached. The next sample after zero generates an interrupt and re-

loads the Current Count register with the values in the Base registers.

For all data formats except ADPCM, the DMA Base registers must be loaded with the number of samples, minus one, to be transferred between "DMA Interrupts". Stereo data contains twice as many bytes as mono data but the same number of samples. Likewise, 16-bit data contains twice the number of bytes as 8-bit data but the same number of samples. The equation for loading the DMA Base registers is:

DMA Base register<sub>16</sub> =  $N_S - 1$

Where N<sub>S</sub> is the number of samples transferred between interrupts and the "DMA Base register<sub>16</sub>" consists of the concatenation of the upper and lower DMA Base registers.

For the ADPCM data format, the contents of the DMA Base registers are calculated differently from any other data format. In the ADPCM format the data is transferred 4 bytes at a time. Each four byte word transferred, decrements the DMA Current Count register. The Base registers must be loaded with the number of BYTES to be transferred between "DMA interrupts", divided by four, minus one. The same calculation is used whether the data format is stereo or mono ADPCM. The 4-byte word contains 8 mono ADPCM samples or 4 stereo ADPCM samples. The equation for loading the DMA Base registers is:

DMA Base register<sub>16</sub> =  $N_b/4 - 1$

Where  $N_b$  is the number of BYTES transferred between interrupts and the "DMA Base register<sub>16</sub>" consists of the concatenation of the upper and lower DMA Base registers.

Playback DMA Registers

The playback DMA registers (I14/15) are used for sending playback data to the DACs in

MODE 2. In MODE 1 or when SDC = 1, these registers (I14/15) are used for both playback and capture.

When the playback Current Count register rolls under, the Playback Interrupt bit, PI, (I24) is set causing the INT bit (R2) to be set. The interrupt is cleared by a write of any value to the Status register (R2), or writing a "0" to the Playback Interrupt bit, PI (I24). When SDC = 1, PI reflects the status of I14/I15 for both playback and capture.

# Capture DMA Registers

The Capture DMA Base registers (I30/31) provide a second pair of Base registers that allow full-duplex DMA operation. With full-duplex operation, capture and playback can occur simultaneously utilizing different DMA channels. These registers are only used in MODE 2 with SDC = 0. If SDC in I9 is set, I14/I15 are used for Capture DMA Base registers.

When the capture Current Count register rolls under, the Capture Interrupt bit, CI, (I24) is set causing the INT bit (R2) to be set. The interrupt is cleared by a write of any value to the Status register (R2), or by writing a "0" to the Capture Interrupt bit, CI (I24). The CI bit is tied to the Capture DMA base registers; therefore, when SDC = 1, the CI bit is non-functional.

# Digital Loopback

Digital Loopback is enabled via the LBE bit in the Loopback Control register (I13). This loopback routes the digital data from the ADCs to the DACs. This loopback can be digitally attenuated via additional bits in the Loopback Control register (I13). Loopback is then summed with DAC data supplied at the digital bus interface. When loopback is enabled, it will "freerun" synchronous with the sample rate. The digital loopback is shown in the CS4231A Block Diagram on the front cover. This loopback can be

used to mix the incoming microphone data with data from the DACs. Since the CS4231A allows selection of different data formats between capture and playback, if the capture channel is set to mono and the playback channel set to stereo, the mono input (mic) data will be mixed into both channels of the output mixer.

If the sum of the loopback and bus data are greater than full scale, CS4231A will send the appropriate full scale value to the DACs (clipping).

# Timer Registers

The Timer Base registers are provided for synchronization, watch dog, and other functions where a high resolution time reference is required. This counter is 16 bits and the exact time base, listed in the register description, is determined by the crystal selected.

When the Timer Enable bit TE, in the Alternate Feature Enable register (I16) is clear, the timer does not count. The Timer is set by loading the Upper and then the Lower Base register to the appropriate values and setting TE. When the Timer Lower Base register (I20) is loaded, the entire 16-bit value is loaded into an internal Current Count register which is decremented at approximately a 10 usec rate. When the value of the Current Count register reaches zero, the Timer Interrupt bit, TI, in I24 is set, and and interrupt is generated if the INT bit (R2) is set. On the next timer clock, the value of the Timer Base registers are automatically loaded into the internal Current Count register which begin counting to zero again. The interrupt is cleared by any write to the Status register (R2) or by writing a "0" to the Timer Interrupt bit, TI, in the Alternate Feature Status register (I24). Since the timer will continue counting down while an interrupt is pending, interrupts will be generated at fixed time intervals regardless of the time required to service the interrupt (assuming the interrupt is

serviced before the next timer interrupt is generated).

#### Interrupts

The INT bit of the Status register (R2) always reflects the status of the CS4231A internal interrupt state. A roll-over from any Current Count register (DMA playback, DMA capture, or Timer) sets the INT bit. This bit remains set until cleared by a write of ANY value to Status register (R2), or by clearing the appropriate bit or bits (PI, CI, TI) in the Alternate Feature Status register (I24).

The Interrupt Enable (IEN) bit in the Pin Control register (I10) determines whether the interrupt pin responds to the interrupt event in the CS4231A. When the IEN bit is 0, the interrupt is masked and the IRQ pin of the CS4231A is forced low. However, the INT bit in the Status register (R2) always responds to the counter.

# **Error Conditions**

Data overrun or underrun could occur if data is not supplied to or read from the CS4231A in the appropriate amount of time. The amount of time for such data transfers depends on the frequency selected within the CS4231A.

Should an overrun condition occur during data capture, the last whole sample (before the overrun condition) will be read by the DMA interface. A sample will not be overwritten while the DMA interface is in the process of transferring the sample.

Should an underrun condition occur in a play-back case, the last valid sample will be output (assuming DACZ=0) to the DACs which will mask short duration error conditions. When the next complete sample arrives from the host computer the data stream will resume on the next sample clock.

#### CS4231A REGISTER MAPPING

MODE 2 which allows access to indirect registers 16 through 31 and enables all the features of the CS4231A.

|    | Addr. | Register Name          |  |

|----|-------|------------------------|--|

| R0 | 0     | Index Address register |  |

| R1 | 1     | Indexed Data register  |  |

| R2 | 2     | Status register        |  |

| R3 | 3     | PIO Data register      |  |

**Table 1. Direct Registers**

The two address pins of the CS4231A allow access to four 8-bit registers. Two of these registers provide indirect access to more CS4231A registers via an index register. The other two registers provide status information and allow audio data to be transferred to and from the CS4231A without using DMA cycles or indexing.

# Physical Mapping

The PIO registers are I/O mapped via four locations. Two address pins provide access to all of the CS4231A's registers. The four direct registers are shown in Table 1. The first two direct registers are used to access 32 indirect registers shown in Table 2. As indicated by the arrows, the Index Address register (R0) points to the indirect register that is accessed through the Indexed Data register (R1).

This section describes all the direct and indirect registers. Table 3 details a summary of each bit in each register with Tables 4 through 10 illustrating the majority of decoding needed when programming the CS4231A and are included for reference. Tables 4 through 8 indicate gain settings at internal nodes. If OLB= 1 then the output will reflect the gain setting. If OLB= 0, the output will be attenuated by 3 dB as indicated in the specifications. The CS4231A powers up into the reset state which is defined as MODE 1. MODE 1 is backwards compatible with the CS4248 and only allows access to the first 16 indirect registers. Setting the MODE2 bit in the MODE and ID register (I12) enables

| ndex       | Register Name                   |

|------------|---------------------------------|

| 10         | Left ADC Input Control          |

| l1         | Right ADC Input Control         |

| 12         | Left Aux #1 Input Control       |

| I3         | Right Aux #1 Input Control      |

| 14         | Left Aux #2 Input Control       |

| <b>I</b> 5 | Right Aux #2 Input Control      |

| 16         | Left DAC Output Control         |

| <b>I</b> 7 | Right DAC Output Control        |

| 18         | Fs & Playback Data Format       |

| 19         | Interface Configuration         |

| I10        | Pin Control                     |

| l11        | Error Status and Initialization |

| l12        | MODE and ID (MODE2 bit)         |

| l13        | Loopback Control                |

| l14        | Playback Upper Base Count       |

| l15        | Playback Lower Base Count       |

| l16        | Alternate Feature Enable I      |

| l17        | Alternate Feature Enable II     |

| l18        | Left Line Input Control         |

| l19        | Right Line Input Control        |

| 120        | Timer Low Base                  |

| I21        | Timer High Base                 |

| 122        | RESERVED                        |

| 123        | Alternate Feature Enable III    |

| 124        | Alternate Feature Status        |

| 125        | Version / Chip ID               |

| 126        | Mono Input & Output Control     |

| 127        | RESERVED                        |

| 128        | Capture Data Format             |

| 129        | RESERVED                        |

| I30        | Capture Upper Base Count        |

| I31        | Capture Lower Base Count        |

| ·          |                                 |

**Table 2. Indirect Registers**

| Index Addres  D7 D6  INIT MCE                                                                         | ss Register (R0) <b>D5 D4 D3 D2 D1 D0</b> TRD IA4 IA3 IA2 IA1 IA0                                                                                                               | Indexed Date D7 D6 ID7 ID6                                                                                           | D5       D4       D3       D2       D1       D0         ID5       ID4       ID3       ID2       ID1       ID0                                                                              |  |  |  |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IA3-IA0                                                                                               | Index Address: These bits define the address of the CS4231A register accessed by the Indexed Data register (R1). These bits are read/write.                                     | ID7-ID0 Indexed Data register: These bits are the indirect register referenced by the Indexed Address register (R0). |                                                                                                                                                                                            |  |  |  |

| IA4                                                                                                   | Allows access to indirect registers 16 - 31. Only available in MODE 2. In MODE 1,this bit is reserved.                                                                          | During initialization and power down, this register can NOT be written and is always read 10000000 (80h)             |                                                                                                                                                                                            |  |  |  |

| TRD                                                                                                   | Transfer Request Disable: This bit, when set, causes DMA transfers to cease when the INT bit of the status register is set. Independent for playback and capture interrupts.    | Status Regist  D7 D6  CU/L CL/R                                                                                      | ter (R2, Read Only)  D5 D4 D3 D2 D1 D0    CRDY   SER   PU/L   PL/R   PRDY   INT                                                                                                            |  |  |  |

|                                                                                                       | <ul><li>0 - Transfers Enabled (PDRQ and CDRQ occur uninhibited)</li><li>1 - Transfers Disabled (PDRQ and CDRQ only occur if INT bit is 0)</li></ul>                             | INT                                                                                                                  | Interrupt Status: This indicates the status of the internal interrupt logic of the CS4231A. This bit is cleared by any write of any value to this register. The ISA hit of the Ric Control |  |  |  |